# **Florida State University Libraries**

Electronic Theses, Treatises and Dissertations

The Graduate School

2004

# Using De-Optimization to Re-Optimize Code

Stephen R. Hines

# THE FLORIDA STATE UNIVERSITY

# COLLEGE OF ARTS AND SCIENCES

USING DE-OPTIMIZATION TO RE-OPTIMIZE CODE

By

# **STEPHEN R. HINES**

A Thesis submitted to the Department of Computer Science in partial fulfillment of the requirements for the degree of Master of Science

> Degree Awarded: Summer Semester, 2004

The members of the Committee approve the thesis of Stephen R. Hines defended on April 30, 2004.

David Whalley Professor Directing Thesis

Gary Tyson Committee Member

Xin Yuan Committee Member

The Office of Graduate Studies has verified and approved the above named committee members.

To Mom, Dad, and Frank ...

# ACKNOWLEDGMENTS

I am very grateful for the help of my advisor, Dr. David Whalley. Without you, this thesis would not have been possible. Thank you for believing in me, as well as inspiring me to work hard to achieve my goals.

I would also like to thank the other members of the Compilers Group (Prasad Kulkarni, Bill Kreahling, Clint Whaley, Wankang Zhao) for their assistance. This work would have been extraordinarily difficult without your insight and your friendship.

I would like to extend a big thanks to my family and friends for their unwavering love and support. You may not understand all of the complexities involved in my research, but I certainly learned that you are always willing to listen to me. I am truly blessed to have each of you in my life.

# TABLE OF CONTENTS

| List | of Tables                                                                                                                                                                                                                                                                                                                                                                       | vii                                                        |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| List | of Figures                                                                                                                                                                                                                                                                                                                                                                      | viii                                                       |

| Abs  | stract                                                                                                                                                                                                                                                                                                                                                                          | ix                                                         |

| 1.   | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                    | 1                                                          |

| 2.   | EXPERIMENTAL SETTING                                                                                                                                                                                                                                                                                                                                                            | <b>5</b>                                                   |

|      | <ul> <li>2.1 VPO Interactive System for Tuning<br/>Applications (VISTA)</li> <li>2.1.1 Very Portable Optimizer (VPO)</li> <li>2.1.2 Searching for Effective Phase Sequences</li> <li>2.2 Hardware and Software Platform</li> <li>2.2.1 MiBench Embedded Applications<br/>Benchmark Suite</li> <li>2.2.2 Generating Assembly Code</li> <li>2.3 Experimental Test Plan</li> </ul> | $5 \\ 6 \\ 7 \\ 9 \\ 10 \\ 11$                             |

| 3.   | DEVELOPMENT OF ASM2RTL TOOLS                                                                                                                                                                                                                                                                                                                                                    | 14                                                         |

|      | <ul> <li>3.1 Assembly Translation and Re-optimization</li> <li>3.2 Preservation of Program Semantics</li> <li>3.2.1 Information Loss</li> <li>3.2.2 Local Variables</li> <li>3.2.3 Calling Conventions</li> <li>3.4 Translation Difficulties</li> <li>3.4.1 Memory Consistency</li> <li>3.4.2 Following Calling Conventions</li> <li>3.5 Additional Translators</li> </ul>      | $14 \\ 16 \\ 17 \\ 18 \\ 19 \\ 21 \\ 21 \\ 23 \\ 24 \\ 25$ |

| 4.   | DEVELOPMENT OF DE-OPTIMIZATIONS                                                                                                                                                                                                                                                                                                                                                 | 27                                                         |

|      | <ul> <li>4.1 Loop-Invariant Code Motion</li></ul>                                                                                                                                                                                                                                                                                                                               | 27<br>28<br>29<br>32<br>33<br>34                           |

|     | <ul> <li>4.2.3 De-optimizing Register Allocation</li></ul>                                                                                                                                                                                                           | $36 \\ 39 \\ 43 \\ 44 \\ 45$            |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 5.  | REVERSE COPY PROPAGATION                                                                                                                                                                                                                                             | 47                                      |

|     | <ul> <li>5.1 Motivation for Reverse Copy Propagation</li></ul>                                                                                                                                                                                                       | 47<br>50<br>53                          |

| 6.  | EXPERIMENTAL TESTING                                                                                                                                                                                                                                                 | <b>56</b>                               |

|     | <ul> <li>6.1 Experimental Results</li> <li>6.2 Discussion of Results</li> <li>6.2.1 Re-optimization Benefits</li> <li>6.2.2 Effectiveness of Register Re-assignment</li> <li>6.2.3 Genetic Algorithm Behavior</li> <li>6.2.4 Dynamic Execution Statistics</li> </ul> | 56<br>58<br>59<br>59<br>59<br>60        |

| 7.  | RELATED WORK                                                                                                                                                                                                                                                         | 62                                      |

| 8.  | ADDITIONAL BENEFITS OF THIS WORK                                                                                                                                                                                                                                     | 65                                      |

|     | <ul> <li>8.1 Use of ASM2RTL in DSP-driven Labs</li> <li>8.2 Detecting Homomorphic Code in VISTA</li> </ul>                                                                                                                                                           | $\begin{array}{c} 65\\ 66\end{array}$   |

| 9.  | FUTURE WORK                                                                                                                                                                                                                                                          | 68                                      |

|     | <ul><li>9.1 More Extensive Experiments</li><li>9.2 Improving De-optimization</li></ul>                                                                                                                                                                               | $\begin{array}{c} 68 \\ 69 \end{array}$ |

| 10. | CONCLUSIONS                                                                                                                                                                                                                                                          | 71                                      |

| RE  | FERENCES                                                                                                                                                                                                                                                             | 73                                      |

| BIC | OGRAPHICAL SKETCH                                                                                                                                                                                                                                                    | 75                                      |

# LIST OF TABLES

| 2.1 | MiBench Benchmarks Used for Experiments                           | 9  |

|-----|-------------------------------------------------------------------|----|

| 2.2 | GCC Optimization Flags                                            | 11 |

| 2.3 | VISTA Genetic Algorithm Candidate and Required Phases             | 13 |

| 6.1 | Effect of De-optimization on Static and Dynamic Instruction Count | 57 |

# LIST OF FIGURES

| 1.1 | Assembly De-optimization and Re-optimization         | 3  |

|-----|------------------------------------------------------|----|

| 2.1 | VISTA Genetic Algorithm Search Parameters            | 7  |

| 2.2 | VISTA Genetic Algorithm Search (In Progress)         | 8  |

| 3.1 | Iterative Re-optimization of Assembly Code           | 16 |

| 3.2 | Local Variable Confusion                             | 18 |

| 3.3 | ASM2RTL Program Structure                            | 20 |

| 3.4 | Local Variable Reconstruction                        | 22 |

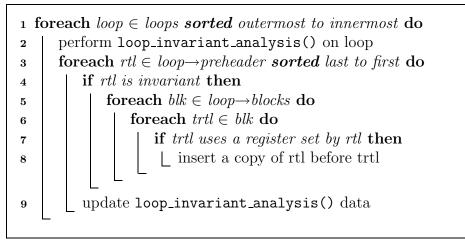

| 4.1 | De-optimize Loop-Invariant Code Motion               | 30 |

| 4.2 | De-optimizing Loop-Invariant Code Motion             | 31 |

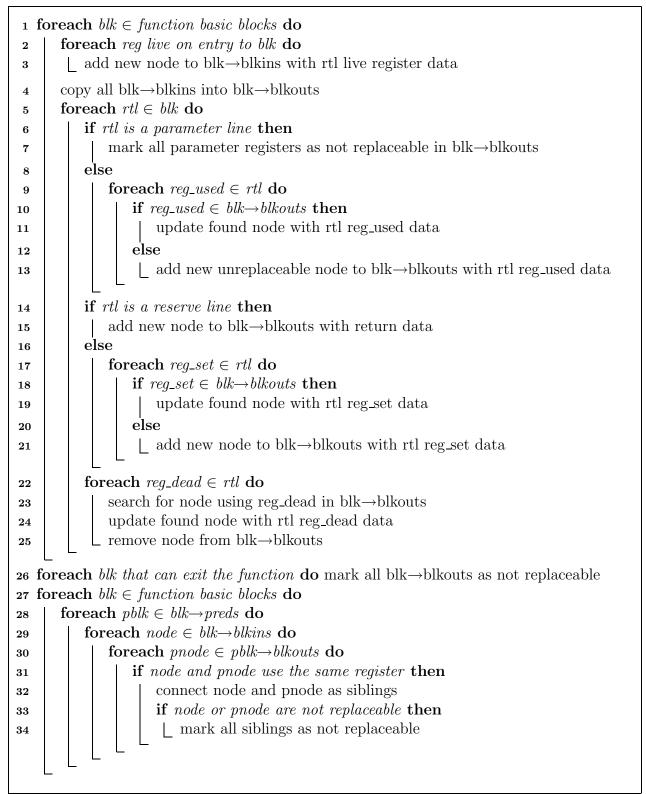

| 4.3 | Constructing a Register Interference Graph           | 35 |

| 4.4 | De-optimize Register Allocation                      | 38 |

| 4.5 | Dequeue from Dijkstra Benchmark                      | 39 |

| 4.6 | Dequeue Prior To De-optimizing Register Allocation   | 40 |

| 4.7 | Dequeue After De-optimization of Register Allocation | 41 |

| 4.8 | Dequeue After Re-performing Register Assignment      | 43 |

| 4.9 | Dequeue After Additional Optimizations               | 44 |

| 5.1 | Register Re-assignment with Keymatch                 | 49 |

| 5.2 | Reverse Copy Propagation                             | 51 |

| 5.3 | Backward Scan                                        | 52 |

| 5.4 | Forward Scan                                         | 53 |

| 5.5 | Reverse Copy Propagation with Keymatch               | 55 |

| 8.1 | Two Functions with Homomorphic Code                  | 67 |

# ABSTRACT

The nature of embedded systems development places a great deal of importance on meeting strict requirements in areas such as static code size, power consumption, and execution time. Due to this, embedded developers frequently generate and tune assembly code for applications by hand. The phase ordering problem is a well-known problem affecting the design of optimizing compilers. VISTA is an optimizing compiler framework that employs iteration of optimization phase sequences and a genetic algorithm search for effective phase sequences in an effort to minimize the effects of the phase ordering problem. Hand-generated code is susceptible to an analogous problem to phase ordering, but there has been little research in mitigating its effect on the quality of the generated code. One approach for adjusting the phase ordering of such previously optimized code is to de-optimize the code by undoing the potential work done by prior optimization phases. This thesis presents an extension of the VISTA framework for investigating the effect and potential benefit of performing de-optimization before re-optimizing assembly code. The construction of a translator tool suite for the purpose of converting assembly code to the VISTA RTL input format is discussed. The design and implementation of algorithms for de-optimization of both loop-invariant code motion and register allocation, along with results of performing experiments regarding de-optimization and re-optimization of previously generated assembly code are also presented.

# CHAPTER 1

# INTRODUCTION

The phase ordering problem is a long-standing problem involved in the development of compilers and related tools [20]. Simply put, the phase ordering problem is that there exists no single sequence of optimization phases that will produce optimal code for every function in every application on every architecture. Different optimizations can enable or disable further optimizations depending on the characteristics of the current function being compiled as well as the target architecture [21]. These enabling or disabling factors can greatly impact the design and implementation of optimizing compilers. One of the most critical enabling or disabling factors is register pressure. Many optimization phases consume registers, thus increasing register pressure. Optimization phases performed after this point will then have fewer available registers to use. Depending on the chosen optimization phase order, later phases may be prohibited from having any effect at all. Embedded systems are even at greater risk of trouble due to the phase ordering problem, since these systems typically have non-orthogonal instruction sets and fewer registers, contributing to even greater register pressure.

One approach towards minimizing the effects of the phase ordering problem is to produce a compiler with the ability to apply phases repeatedly and in any given order. The Very Portable Optimizer (VPO) was developed in an attempt to provide these exact features [1]. VISTA (VPO Interactive System for Tuning Applications) is an enhancement developed for VPO to provide a graphical interactive compilation framework which application developers can use to finely tune generated code [22]. VISTA provides static and dynamic measurement information to allow the programmer to more effectively guide the optimization process [13]. Additionally, the VISTA framework supports automatic tuning of code through the use of static and dynamic profile data combined with a genetic algorithm search for effective phase sequence orderings [15]. All of these features make VISTA an attractive environment for the study of optimizing compiler technology.

Embedded devices are experiencing a great surge in popularity. As the demand for embedded devices increases, so too does the demand for embedded software development. With embedded software development, size and timing constraints are both more important and more stringent than they are in traditional software. This increased focus forces a great deal of embedded applications development to be done using assembly language, since the ability to hand-tune code typically produces smaller and faster executables than comparable high-level languages with good optimizing compilers.

Hand-generated assembly code may appear to be an adequate solution for the requirements of embedded software development, however it is still subject to the phase ordering problem albeit in a slightly different manner. Clearly the majority of optimization phases need not be performed in exactly the same manner by an assembly programmer who is hand-coding a function. Transformations from different optimization phases can be mixed and combined at many different points during the code generation and hand tuning process. Thus there is not truly an explicit phase ordering being applied to the function. Instead, the programmer modifies the code based on intuitions and educated decisions in an attempt to decrease the static and dynamic instruction counts. However these judgments are clearly similar to phase ordering decisions made by an optimizing compiler, so it is possible that a better solution exists even with hand-tuned assembly code.

It is thus natural to attempt to alleviate the phase ordering problem with hand-generated assembly code by making some modifications to the facilities available in the VISTA framework. First a translator must be constructed to convert the assembly code to an input format which VISTA can understand. To handle the phase ordering problem, the concept of de-optimization will be applied. Prior optimizations that affect the phase ordering problem can be undone in a safe manner, so that different phase sequences can then be applied and tested. For the purpose of this thesis, both *loop-invariant code motion* and *register allocation* will be de-optimized since they have a great impact on register pressure and thus the phase ordering problem. Other optimizations were not selected because they either do not have much of an impact on the phase ordering problem (*branch chaining*), or there is no way to reconstruct the necessary information (*dead assignment elimination*). After performing

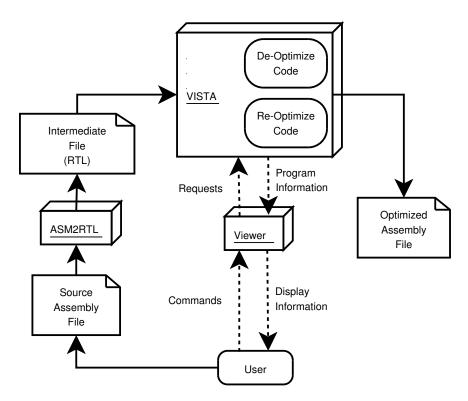

Figure 1.1: Assembly De-optimization and Re-optimization

the required de-optimizations, VISTA can then be instructed to automatically return the de-optimized code sequence using its genetic algorithm search for effective optimization sequences. Figure 1.1 shows the process of re-optimizing assembly code with VISTA.

The rest of this thesis can be broken down as follows: Chapter 2 presents additional preliminary information, including a detailed look at the VISTA framework, which will be used for all testing. The next chapter discusses the process of assembly translation, including the implementation of the ASM2RTL translator suite for converting assembly source code to the VISTA RTL format. Chapter 4 focuses on the actual design and development of de-optimizations within the VISTA framework. Chapter 5 describes the optimization *reverse copy propagation*, which was added to VISTA to improve de-optimized and re-optimized code. The results of performing the proposed experiments are then examined, along with a discussion of the analyzed data. Related work is then reviewed for the areas of assembly translation and de-optimization. Additional benefits of the work done in this thesis are highlighted in Chapter 8. Chapter 9 considers some of the potential future improvements

that can be made to the de-optimization strategy. The final chapter contains concluding remarks regarding the use of de-optimizations for re-optimizing code.

# CHAPTER 2

# EXPERIMENTAL SETTING

The general setup for the de-optimization experiment is described in detail in this chapter. The first section discusses VISTA, the compiler framework for which the proposed de-optimizations will be implemented and tested. The next section contains information concerning the necessary hardware and software for adequately testing the de-optimizations. This also includes detailed descriptions of the benchmarks as well as the compilers used for the experiment. The last section describes the actual test plan which will be used to evaluate the potential effects of de-optimization on the optimization process.

# 2.1 VPO Interactive System for Tuning Applications (VISTA)

In order to investigate the potential benefits of de-optimization with respect to resequencing optimization phases, it was necessary to modify the VISTA (VPO Interactive System for Tuning Applications) compiler framework [22, 15]. VISTA was developed as an interactive compiler that would allow a knowledgeable programmer to finely tune the optimization phase order performed on a given function. To facilitate this, VISTA provides a graphical interface that interacts with a VPO (Very Portable Optimizer) backend. Using this GUI, a programmer can tailor the phase sequence based on immediate performance feedback information generated using EASE (Environment for Architecture Study and Experimentation). However the most attractive feature of VISTA is the ability to automatically search for effective phase sequences using a genetic algorithm. This is particularly beneficial in the case of attempting to reapply transformations on de-optimized assembly code, since we are assuming that the original phase ordering may have been suboptimal.

#### 2.1.1 Very Portable Optimizer (VPO)

A fundamental component of VISTA is VPO, the actual compiler backend with which it communicates. VPO [2] was designed to be both portable and efficient, accepting an intermediate language known as RTLs (Register Transfer Lists), and producing assembly code. These RTLs provide a machine-independent representation of the effects of machine instructions. By operating on these RTLs, various code-improving transformations found in VPO can be written in a machine-independent manner (e.g. loop-invariant code motion), with only a small portion of the code requiring any information about the specifications of the target machine. Thus the amount of work necessary for porting VPO to a new architecture is reduced.

VPO also incorporates EASE (Environment for Architecture Study and Experimentation) [7] for instrumenting generated assembly files to collect performance data. Both static information (code size) and dynamic information (instructions executed, memory references) can be collected through the use of this profile data. VISTA enables the programmer to query these frequency measures at any point during the compilation process, and thus facilitates fine tuning of the code.

#### 2.1.2 Searching for Effective Phase Sequences

Due to the nature of embedded application development, longer compile times are often tolerated to allow further improvements to the generated code, since code size and timing requirements are typically very inflexible. Evolutionary algorithms are effective in dealing with large search spaces for which the interaction between parameters is not well understood. Since the phase ordering problem has been characterized in this manner [6], a genetic algorithm approximation is a good solution. The VISTA framework provides such a genetic algorithm search for effective phase sequences [13, 15, 14].

Figure 2.1 depicts the genetic algorithm search window with various parameters that are able to be adjusted by the programmer. The parameters include the optimization phases available to the algorithm, the maximum number of phases to perform, the population size, the number of generations, the type of search to perform, as well the fitness criteria to use in evaluating the phase sequences. When selecting the fitness criteria, the programmer

| SelComb Query       | *******      | •••×                       |

|---------------------|--------------|----------------------------|

| No. of Phases:      | 3            | Search Option:             |

| Sequence Length: 10 |              | O Exhaustive Search        |

|                     |              | Biased Sampling Search     |

| Weight Factors:     |              | O Permutation Search       |

| Insts Executed 50   | Code Size 50 | Population Size: 20        |

| 0 20 40 6           | 0 80 100     | Number of Generations: 100 |

|                     | ok           | <b>cancel</b> help         |

Figure 2.1: VISTA Genetic Algorithm Search Parameters

can choose between optimizing for code size, instructions executed, or a mixture of both. Optimization phase sequences are then tested systematically by the genetic algorithm to locate the most beneficial ordering it can find based on the fitness criteria selected.

The genetic algorithm can also be prematurely stopped by the programmer if the desired level of optimizations are achieved before completing the entire specified search. Figure 2.2 shows a search in progress after 448 attempted sequences. Note that invalid sequences are displayed and recorded to assist in the debugging of new optimizations and features added to VISTA. Both the current sequence being tested and the best found sequence are displayed using simple letters to represent the various optimization phases. Statistics about the performance of the best sequence can be found at the bottom of the window. Sequence 317 produces code that is 47% of the original code size as well as only executing 48.4% of its original instructions. In this example, the fitness criteria is mixed 50%/50% for static and dynamic count measures, thus showing a 47.7% relative fitness for the best sequence found in the search to this point.

# 2.2 Hardware and Software Platform

The proposed modifications to VISTA were tested using an Intel StrongARM SA-110 processor running Netwinder Linux. Due to the low clock speed of the StrongARM processor, several other machines were used for cross-compiling for static code size only if the function being optimized was not executed by an application given the sample test data. In such

| SelComb Result          | ******************   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | · O x |

|-------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|                         | Percent Complete:    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|                         | 22%                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| Combinations Completed: |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| Valid: 448              | Invalid: 0           | Total: 448/2000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| Valiu. 440              |                      | Total. 448/2000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| Best Sequence:          | Libmesskds           | Seq. Num.: 317                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

|                         |                      | an and a second s |       |

| Current Sequence:       | bumeusrkhq           | Improvement: 48.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

| Relative Improvements:  |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| Code Size: 47.0         | Insts Executed: 48.4 | Overall: 47.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

|                         | 10.1                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|                         | Stop                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|                         |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

Figure 2.2: VISTA Genetic Algorithm Search (In Progress)

cases, only the static code size measure could be extracted and thus used to guide VISTA in the automatic tuning of the code. VISTA typically uses the dynamic instruction count as a tie-breaker for cases where the function is executed by the application. The machines used for cross-compiling included a Sun Ultra SPARC III as well as an Athlon XP.

Due to the proprietary nature of most embedded applications, it is quite a challenge to find hand-generated assembly programs that are representative of the typical workload. To the best of our knowledge, there are no currently available embedded benchmark suites written in assembly code. Rather than devising a new set of hand-tuned assembly benchmarks for embedded systems, an optimizing compiler could be used instead with a comparable existing high-level source code benchmark suite. Although using actual hand-tuned assembly code would be better, the use of known optimization techniques with a known benchmark suite provides a legitimate testing framework for evaluating the effects of de-optimization when re-optimizing code.

#### 2.2.1 MiBench Embedded Applications Benchmark Suite

In order to effectively gauge the effectiveness of performing de-optimizations on optimized assembly, we selected an appropriate benchmark suite. The applications available in the MiBench embedded applications benchmark suite are described as representative of common programs used in embedded systems [9]. The suite consists of several programs from the following six categories: Automotive/Industrial, Network, Telecommunications, Consumer, Security, and Office. For the experiments performed, one application was selected from each area as shown in Table 2.1.

| Table 2.1. Wildenen Benenmarks ebed for Experiments |              |                                    |

|-----------------------------------------------------|--------------|------------------------------------|

| Category                                            | Program      | Description                        |

| Automotive/Industrial                               | bitcount     | Bit manipulation tests             |

| Network                                             | dijkstra     | Dijkstra's shortest path algorithm |

| Telecomm                                            | fft          | Computes a Fast Fourier Transform  |

| Consumer                                            | jpeg         | Creates a jpeg image from a ppm    |

| Security                                            | sha          | NIST Secure Hash Algorithm         |

| Office                                              | stringsearch | String pattern matcher             |

Table 2.1. MiBench Benchmarks Used for Experiments

Three benchmark programs required minor changes in order to translate and compile correctly using the modified version of VISTA. In the benchmark *stringsearch*, a large local array was changed to static in order to not require additional information to be supplied to the translator. This change does not impact the experimental comparison since neither GCC nor VISTA modify the placement of local arrays on the stack. In the *fft* benchmark, several functions were adjusted to pass a pointer to a data structure containing floating-point arguments instead of each individual argument. This change was necessary as calling conventions for the ARM are complex when dealing with floating-point arguments that get passed in registers and on the stack. This further complicates the process of translating these parameters appropriately. Performing this fix will inhibit performance slightly as an additional pointer dereference is now required to access each argument. This fix helps during translation to reduce the amount of outside information necessary for correct behavior. Additionally, for the *jpeg* benchmark, the function *parse\_switches* was not able to be tested using VISTA. This was due to a problem with code expansion during the translation pushing global variable references further from the actual global variable locations. Further discussion of assembly code requirements for translation and information loss is available in Chapter 3 and Chapter 4.

#### 2.2.2 Generating Assembly Code

In order to allow a fair test of the the proposed de-optimization strategy, it was necessary to run each program through an optimizing compiler. Each of the programs from the MiBench suite was compiled and optimized using the GNU Compiler Collection's C compiler version 3.3 [8] for the ARM. The exact command line used to compile each of the C source files was as follows:

#### gcc -O2 -S -c -fno-optimize-sibling-calls -ffixed-lr -ffixed-fp filename.c

This command line can be broken down as shown in Table 2.2. The options specified are necessary to provide for as little information loss as possible when translating from the assembly. Level 2 optimization allows a fair comparison to hand-generated assembly since it does not invoke additional phases that will contribute to increased space requirements. The -S and -c flags force GCC to generate assembly code as output. Translating from object code is possible, but would add an additional unnecessary complexity to the translation process for our purposes.

The -f flags that were selected disable specific phases of the -O2 optimization process. Optimizing sibling calls is a transformation that allows leaf or sibling functions to omit save and restore instructions. Allowing GCC to perform these optimizations makes it harder for the translator to analyze where the function exits. Additionally VISTA will automatically re-perform this translation on the code both for the GCC baseline code as well as the experimental code. The two *-ffixed* flags force GCC to disallow the use of these registers as general purpose registers. This is necessary to perform a fair comparison since VISTA currently does not support using either the Frame Pointer or the Link Register in a different manner than that for which they were intended.

| Flag                        | Meaning                                    |

|-----------------------------|--------------------------------------------|

| -O2                         | Level 2 optimizations (Standard)           |

| -S                          | Generate assembly file but do not assemble |

| -C                          | Compile and do not link                    |

| -fno-optimize-sibling-calls | Do not perform optimizations for leaf      |

|                             | or sibling functions                       |

| -ffixed-lr                  | Do not use the Link Register (LR)          |

|                             | as a general purpose register              |

| -ffixed-fp                  | Do not use the Frame Pointer (FP)          |

|                             | as a general purpose register              |

Table 2.2. GCC Optimization Flags

#### 2.3 Experimental Test Plan

Using the MiBench benchmark programs, each GCC-generated assembly file is translated to RTL format using the ASM2RTL translator as discussed in Chapter 3. These input files are then compiled using VISTA and tested for correctness. These results form the baseline for our further measurements. After verifying the newly translated code, each function is tested for immediate code improvements from the traditional optimization phases performed by VISTA. Additional optimization phase orderings are selected using the genetic algorithm search with three different fitness criteria: 50% code size/50% dynamic instruction count, 100% code size, and 100% dynamic instruction count. Next the de-optimizations are turned on before applying further VISTA optimization phases, and data is again collected using the three fitness criteria. For the de-optimizations, first loop-invariant code motion is undone, followed by the de-optimization of register allocation. Further details of the entire de-optimization process are described in Chapter 4. For each of the test cases, 14 optimization phases are available from which the genetic algorithm can choose. These phases are described in greater detail in the top portion of Table 2.3. The bottom portion of the table displays two required phases for the genetic algorithm. *Register assignment* is performed after *register allocation* is de-optimized and *fix entry exit* is performed as the final phase for each function compiled.

From the data collected, comparisons will be made between code size and dynamic instruction count of both the optimized code and the de-optimized plus re-optimized code for each benchmark. The potential benefit of assembly translation and further optimization can be shown between the GCC-generated code and the results of optimizing that code. Potential benefits of de-optimization plus re-optimization will be shown by comparing with the results of the optimized VISTA translated assembly code.

| Optimization Phase               | Description                                         |

|----------------------------------|-----------------------------------------------------|

| Branch Chaining                  | Replaces a branch or jump target with the target    |

|                                  | of the last jump in a jump chain.                   |

| Common Subexpression Elimination | Eliminates fully redundant calculations which also  |

|                                  | includes constant and copy propagation.             |

| Remove Unreachable Code          | Removes basic blocks that cannot be reached         |

|                                  | from the entry block of the function.               |

| Remove Useless Blocks            | Removes empty basic blocks from the control         |

|                                  | flow graph.                                         |

| Dead Assignment Elimination      | Removes assignments when the assigned value         |

|                                  | is never used.                                      |

| Block Reordering                 | Removes a jump by reordering basic blocks when      |

|                                  | the jump target has only a single predecessor.      |

| Minimize Loop Jumps              | Removes a jump associated with a loop by            |

|                                  | duplicating a portion of the loop.                  |

| Register Allocation              | Replaces references to a variable within a specific |

|                                  | live range with a register.                         |

| Loop Transformations             | Performs loop-invariant code motion, induction      |

|                                  | variable elimination, and loop strength reduction   |

|                                  | on each loop, ordered by loop nesting level.        |

| Merge Basic Blocks               | Merges two consecutive basic blocks $a$ and $b$     |

|                                  | when $a$ is only followed by $b$ and $b$ is only    |

|                                  | preceded by a.                                      |

| Strength Reduction               | Replaces an expensive operation with one or more    |

|                                  | cheaper ones.                                       |

| Reverse Jumps                    | Eliminates an unconditional jump by reversing       |

|                                  | a conditional branch when it branches over          |

|                                  | the jump.                                           |

| Instruction Selection            | Combine instructions together and perform           |

|                                  | constant folding when the combined effect is        |

|                                  | a legal instruction.                                |

| Remove Useless Jumps             | Removes jumps and branches whose target is          |

|                                  | the following block.                                |

| Register Assignment              | Maps all pseudo-registers to hardware registers     |

|                                  | and generates any necessary spill code              |

| Fix Entry Exit                   | Arranges remaining local variables on the stack     |

|                                  | and generates all necessary save and restore code   |

|                                  | for function entry and exit points.                 |

|                                  | Performs predication of RTLs if possible.           |

Table 2.3.

VISTA Genetic Algorithm Candidate and Required Phases

# CHAPTER 3

# DEVELOPMENT OF ASM2RTL TOOLS

This chapter focuses on the translation of assembly source code to the VISTA RTL format, and the ASM2RTL tool suite that was developed to facilitate this process. The first section covers the basics of assembly translation and re-optimization as well as why this can be such an attractive option for embedded applications development. Next we explain some of the problems surrounding the translation process itself, specifically with regard to maintaining program correctness. The next section discusses some implementation strategies to make the tool suite as robust as possible. Difficulties encountered during the translation process as well as the chosen solutions are then presented in the following section. The final section describes additional translators that were developed for use with the ASM2RTL tool suite, but not used for the purposes of this study.

#### 3.1 Assembly Translation and Re-optimization

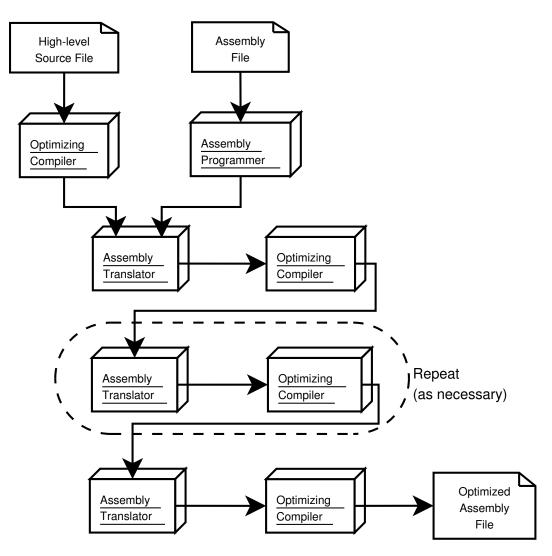

The process of assembly translation discussed in this thesis refers to the conversion of assembly source code to an intermediate language for use with an optimizing compiler. Translation enables an iterative process for re-optimizing programs with potentially different compilers and optimization techniques. SALTO is a tool for assembly transformation and optimization that is employed in such an iterative process [18]. Low-level optimizations are applied to assembly code by SALTO as part of an iterative sequence including both a high-level restructurer and an optimizing compiler. However, only information about the transformations performed by SALTO are passed back to the original optimizing compiler for the next pass. In this way, no translation is performed to convert the assembly code back to the intermediate language. This is slightly different from the proposed strategy for re-optimization presented in this thesis, where optimized assembly code is actually translated into the appropriate intermediate form. Figure 3.1 shows one potential view of an iterative process for the further optimization of assembly source code. One of the main advantages of this arrangement is the ability to use various independent optimizing compilers for each stage of the optimization, so long as an appropriate translator has been constructed for its corresponding intermediate language. A high-level source file can be compiled with a traditional compiler or a hand-tuned assembly file can be used as the initial input to the system. Assembly code is then translated to an intermediate language format and fed to a corresponding optimizing compiler. This process can be be repeated with additional translators and optimizing compilers as many times as necessary. Additional passes could also be substituted with hand-tuning of the assembly code by a programmer. It is easy to see that this scheme can be further extended to incorporate profiling data with each optimizing compiler pass, exposing even further opportunities for fine-tuning the code.

Although performing optimization passes in an iterative manner will be more timeconsuming, the benefit may be invaluable, particularly for applications with strict requirements. Embedded applications can have real-time considerations or code size limitations that must be rigidly adhered to. These types of constraints make complex optimization strategies such as an iterative model attractive since the increased optimization benefits can outweigh the additional overhead cost.

This thesis focuses on the effects and possible benefits of reordering optimization phases via de-optimization and re-optimization. To study this, it was necessary to construct a translator from native ARM assembly code to VISTA RTLs (Register Transfer Lists). This translator is part of a larger suite of ASM2RTL tools, a group of translators in which each converts instructions from a given assembly language to RTLs. The current version of ASM2RTL supports assembly instructions from the Sun Ultra SPARC III, the Texas Instruments TMS320c54x and the Intel StrongARM. Assembly translation to the intermediate RTL form which VISTA accepts appears to be mostly straightforward, but it does contain several potential pitfalls.

Almost every problem that can occur is due to the loss of semantic content needed for correct operation. However there are other potential problems in translation, such as the lack of support from the VPO compiler for a very context-specific instruction (e.g. predicated return instruction). If a compiler cannot produce a particular instruction, it must be replaced

Figure 3.1: Iterative Re-optimization of Assembly Code

by a semantically equivalent sequence of instructions that preserve all other aspects of the current program state.

# 3.2 Preservation of Program Semantics

#### 3.2.1 Information Loss

It is well known that translating from a high level language to assembly language is easier than translating from assembly language back to a high level language. The information contained within a program can be characterized as flowing from its highest level source code down to the final machine code. As a program progresses through various intermediate representations, each lower level form carries less information than preceding higher level forms. Thus it becomes increasingly difficult (if not impossible) to extract the entire original program representation from a low level form. When attempting to reconstruct original semantic content for a compiled program, one problematic area is the detection and characterization of local variables. Another problem is maintaining consistency with the calling conventions of the given instruction set architecture (ISA).

#### 3.2.2 Local Variables

Local variables (or automatic variables) are those which are kept on the run-time stack. Modern ISAs support memory accesses of fixed size increments. As an example the StrongARM supports memory access sizes of 1 byte, 2 bytes, 4 bytes, and 8 bytes. However data that is larger than these sizes can only be accessed by breaking it into pieces that conform with these sizes. Arrays and structures are typically larger than these fixed sizes and are thus handled by moving the necessary pieces into registers using these standard memory-accessing instructions. From a low-level assembly representation of such a program, it is difficult to distinguish between scalar and array data.

This is problematic when doing translation and re-optimization, since the VISTA RTL representation (like most intermediate languages) handles local variables symbolically. This means that the original numeric offset information is lost during the translation, and the ordering of local variables on the stack can change. This reordering can cause the generated code to be semantically incorrect, since local variables larger than 4 bytes may be split apart and spread out on the stack. This is especially true for local structures where certain fields may be manipulated while others are ignored. Calling a function using a pointer to such a split structure would cause other local variables to be incorrectly read and written in memory, since the C language assumes each function uses the same structure layout. The same argument holds for arrays as well, since they are merely a constrained structure where each field is of the same data type.

Figure 3.2 shows an example where optimized ARM assembly code can easily be misinterpreted. The corresponding RTLs are shown as comments to the right of each instruction. Both code snippets come from the function  $fft_float()$  in the FFT benchmark. The top selection of code shows the movement of a double from memory (using the *ldmia*)

|      | Double placed in two integer registers |                              |  |  |

|------|----------------------------------------|------------------------------|--|--|

| Line | Instruction                            | RTLs and Comments            |  |  |

|      |                                        |                              |  |  |

| 1    | add r2, sp, #8                         | r[2]=r[11]+LOC[8];           |  |  |

| 2    | ldmia r2, $\{r2-r3\}$                  | r[2]=R[r[2]];r[3]=R[r[2]+4]; |  |  |

| 3    | str r2, [r5, #16]                      | R[r[5]+16]=r[2];             |  |  |

| 4    | str r3, [r5, #20]                      | R[r[5]+20]=r[3];             |  |  |

|      |                                        |                              |  |  |

|      | Two integer loads coalesced in same manner |                              |  |

|------|--------------------------------------------|------------------------------|--|

| Line | Instruction                                | RTLs and Comments            |  |

|      | •••                                        |                              |  |

| 1    | add r2, sp, #40                            | r[2]=r[11]+LOC[40];          |  |

| 2    | ldmia r2, $\{$ r2, r3 $\}$                 | r[2]=R[r[2]];r[3]=R[r[2]+4]; |  |

| 3    | add r3, r3, r2                             | r[3]=r[3]+r[2];              |  |

|      |                                            |                              |  |

Figure 3.2: Local Variable Confusion

instruction) to two integer registers. This is typically performed for function calls which pass up to the first four parameters (including floating point values) in integer registers. In order to generate correct code, the local variable at location sp+8 must always be considered a double and should not be allowed to be split into two 4-byte integers by VISTA. The bottom portion of code starts off in a similar fashion, loading two registers using a single stack offset with a multiple load instruction. These two registers are then added together, clearly something that is not typical for two 4-byte halves of a double. However it could also be possible that this is part of an integer array where the first two elements are added together (potentially as in a hashing algorithm). As it turns out, these two local variables are indeed just two distinct integers, but that conclusion could not be made without having some additional information provided alongside the assembly code.

#### 3.2.3 Calling Conventions

Another important factor in performing the translation of assembly code to VISTA RTL format is maintaining proper calling conventions. The RTL format requires that registers used as function arguments as well as the size of the arguments passed on the stack be specified explicitly. The registers containing return values must also be specified explicitly. The StrongARM calling conventions can be summarized as follows:

- 1. As many as 4 arguments to a function may be placed in registers using the following order: r0, r1, r2, r3. Additional arguments (beyond 4 words) to functions are to be placed on the runtime stack.

- 2. Floating point arguments will be placed starting in integer registers, and will be split (e.g. r3 and the first argument on the stack) if necessary. The same holds true for structures.

- 3. Variable argument length functions place data in registers similarly, and all additional arguments are pushed onto the runtime stack in reverse order.

- 4. Integer returns are handled using r0. Floating point data is returned via f0. Data structures smaller than 4 words can be returned using as many registers from r0-r3 as necessary. Data larger than this size is handled via an additional address parameter to a structure.

The important considerations here are to make sure that no information is lost during the translation process. If registers that are used as arguments are not specified, then it is possible that VISTA will detect sets to these registers as dead assignments and thus eliminate them. Additionally if registers that contain return values from function calls are not specified appropriately, VISTA will generate spill code around the function call to handle reads from these registers. In each particular case, this will cause incorrect code to be generated for the function, and thus needs to be handled carefully.

# 3.3 Implementation Strategy

The ASM2RTL translator suite was implemented to facilitate retargetability for the source assembly language. Thus there is a large portion of code which is machineindependent. The machine-dependent portions of the code are relatively easy to construct, requiring the modification of several subroutines to perform activities correctly such as operand parsing or assembly instruction identification. The simplified program structure of the translator is displayed in Figure 3.3. Each phase of the translation process will be discussed, but not necessarily in the order in which they took place.

To make the translation process as fast as possible, lines were translated individually in the file, maintaining only a small amount of state information concerning things such as local variables, global variables, function return types and argument counts. Once the instructions were converted to RTL file format, VISTA would be able to reconstruct any additional information it needed by performing the standard analysis phases that it would normally perform with any other supplied input file.

The ASM2RTL translator begins by reading in all necessary configuration information (Line 1). This required information is discussed further in Section 3.4. Using the ASM2RTL translator, each line of the assembly file is parsed and translated into a semantically equivalent sequence of RTLs (Lines 3-5). These RTLs are maintained in a list for output at the end of the program (Line 8). Typically the correspondence is one-to-one, but whenever a global variable or local variable is first encountered, additional RTLs for declarations are also generated. Additionally there are some instructions which are not representable via a single RTL currently and thus the translator will produce an equivalent sequence of instructions instead. Functions are handled one at a time (Line 2), and a post-pass is performed on each function before proceeding to translate the next function (Line 6). After translating each line in the input file, the translator will then proceed to generate the RTL file by emitting all necessary global declarations first (Line 7) and then finally each of the function's RTL lists in order (Line 8).

**Input**: Assembly source file, [function information file], [local structure information] **Output**: Register Transfer List (RTL) representation of file

1 read configuration data

4

$\mathbf{5}$

- 2 foreach function  $\in$  file do

- $\mathbf{3}$  | foreach line  $\in$  function do

- parse line and pass to appropriate handler

- add generated RTLs to function list

- 6 generate appropriate local variable information for RTLs

- 7 output RTL style declarations of globals

- 8 output all RTLs from function lists

#### Figure 3.3: ASM2RTL Program Structure

# **3.4** Translation Difficulties

The two major problems faced when performing translation of assembly code to the VISTA RTL format are maintaining memory consistency and abiding by the calling conventions of the target environment. Both of these problems occur due to the loss of information as the program is converted from a high level source language to assembly language. In some cases, no additional information is necessary to be supplied to the translator, as ASM2RTL can use a few simple techniques to recover such information from the underlying code structure of the assembly file. However, some assembly code is not able to be translated correctly without supplemental information.

#### 3.4.1 Memory Consistency

Maintaining proper memory layout information for local structures is vital to obtaining correct code with VISTA. If structures, arrays or even the two 4-byte halves of a double are allowed to be reorganized with VISTA, then the resulting code will be semantically incorrect. Additionally, memory errors such as segmentation faults and buffer overflows will occur when running the new code. Thus to protect against these types of translation errors, additional information concerning the locations and sizes of local variables is necessary.

This is handled in ASM2RTL by supplying an additional command line parameter along with a file containing function names, followed by lists of structure location, structure size pairs. If specified, this file is read in by ASM2RTL on startup and an additional post-pass for fixing structure locations is invoked before completing the code translation for a particular function.

The method used for producing correct memory layout information is shown in Figure 3.4. First all local variable references that relate to function arguments (either incoming parameters or outgoing arguments) are fixed as static offsets, similarly to the code that the standard VISTA frontend compilers generate (Line 1). Next we perform the structure modifications if they were indeed specified by the user (Line 2). We compare each structure in the list with each local variable offset we have seen (Lines 3-5). If a local is found to be part of a larger data structure, we immediately calculate a new offset for it and replace all references to the original local variable with the structure location plus new offset in the function's RTLs (Line 6). Since all references to this symbolic local variable have been replaced, we can now safely remove it from the local variable symbol table (Line 7).

1 fix all function arguments on the stack as unmodifiable 2 if *fix\_structs\_flag* then for each  $struct \in structs\_list$  do 3 foreach  $var \in local_vars$  do  $\mathbf{4}$ if struct.loc < var < (struct.loc + struct.size) then 5 replace var in RTLs with struct.loc + #(var - struct.loc)6 remove var from local\_vars 7 **s** extract locs from local symbol table 9 sort locs by offset in increasing order 10 foreach  $var \in locs$  do 11 12 prepend local variable declaration RTLs to function list

Figure 3.4: Local Variable Reconstruction

After fixing all local structure references appropriately, the algorithm proceeds to a local variable size auto-detection phase. Each local variable is taken from the symbol table and sorted in increasing order by offset (Lines 8-9). This list can then be traversed in order to access the next neighbor for each particular local offset. Using this method, the size of a local can be calculated as the difference between its next neighbor's offset and its own offset (Lines 10-11). Since we have the total stack size from an initial stack pointer save instruction at the start of the function, we also know the size of the last local variable on the stack. Finally, each local variable has a declaration RTL constructed for it. This RTL is prepended to the current function's list of RTLs (Line 12).

Due to the last phase of reconstruction (Lines 10-11), any array or structure that only has its starting address taken will require no additional information to be supplied in the structs file. This is beneficial in that it reduces the amount of inspection a user must do for the incoming assembly code to detect such memory layout problems. Since array elements are rarely accessed directly by offset (e.g. arr[5]), and structures tend to be dynamically allocated in the heap, the need for user-supplied structure information is minimal.

#### 3.4.2 Following Calling Conventions

A typical RTL input file contains extra information regarding registers and memory locations that are used for special purposes relating to the calling conventions of the StrongARM. Examples of such meta-information RTLs are USELINEs (implicit uses of registers), SETLINEs (implicit sets of registers), PARMLINEs (parameters to a function), CSLINEs (caller save registers), and RESLINEs (registers that are reserved). In order to produce these RTLs properly, it was necessary to detect incoming register arguments, incoming stack-placed arguments, outgoing register arguments, outgoing stack-placed arguments, as well as registers containing return values. It is possible to argue that this data is unnecessary, since all necessary arguments and return values have been set up correctly in the incoming assembly file. This approach could work if VISTA was only to be used for converting the RTLs directly to assembly instructions, however various analyses could be miscalculated without this information and thus code-improving transformations might eliminate necessary instructions.

Live register and variable analysis could be used to detect some incoming parameters and outgoing parameters in a function. To perform live register and variable analysis, the entire control flow graph of the program needs to be constructed. Even at this point, some of the information, such as the size of incoming stack arguments, would still be unavailable as it was lost already at a higher level. Since performing such inter-procedural analysis is time-consuming and may not even yield entirely correct information in these cases, ASM2RTL was set up to strictly perform line-by-line translation. Thus information about live registers and variables for functions needed to be supplied in some other manner than the original input assembly file. To remedy this problem, we allow ASM2RTL to read in configuration information about functions used by the application being translated.

ASM2RTL scans for configuration information about functions when started. Simple text files are parsed for information about function return types and incoming argument sizes in 32-bit words (the smallest unit of allocation for the StrongARM). Data about functions was split into two files, one for globally accessible functions (library or system calls), and one for locally accessible functions (functions defined by the application). This information can then be used during the translation process to reconstruct the appropriate meta-information in RTL format. As an example, knowing the return type of a function allows ASM2RTL to generate appropriate RTLs for maintaining this data as live when exiting the function, so that an RTL updating the return value register is not inappropriately deleted when performing *dead assignment elimination*. Local configuration files can be created by either inspecting the assembly code and interpreting the necessary information, or easily extracted from the original high level source code (if available). The global function configuration file was easily created using library and system call information found in references for the standard C libraries.

Variable length argument functions such as printf() prove to be problematic when translating as well. Because the number of arguments can exceed the number of argument registers, the remaining arguments placed on the stack cannot be reorganized. Thus it is necessary for ASM2RTL to know the exact number of variable parameters used for each call. This is another example of the information lost during the compilation process, so it must be resupplied to the translator. To correct for this, a simple tool was constructed to search for common variable length argument functions in the initial C source files. Using this tool, each variable argument function's name was suffixed with the size of its arguments. In this manner, the configuration file could specify printf5() as having 5 32-bit words of parameters.

Function pointers create another problem since the number of parameters to the actual function is only truly known in the initial source file. In the generated assembly file, the call instruction uses a single register for the actual function address. With ASM2RTL, all calls through function pointers are assumed to use 4 register parameters. Although this would invalidate some C code with more than 4 register parameters, this is not a very common situation, so the tradeoff of having to rewrite offending code is acceptable. Out of all 6 of the tested benchmark programs, there was but a single function that used function pointers, and it only used 3 register parameters.

#### 3.4.3 Translation Tradeoffs

The ASM2RTL tool adopts various strategies for coping with problems that can affect proper translation. Each of these strategies is not without drawbacks. These strategies require the programmer to inspect the supplied input assembly code and extract necessary information from it. There is a tradeoff involved since it is possible to assume a worst case scenario for each of the problems. In this way, no additional information is needed from the programmer, but code improvability is sacrificed.

With the local variable layout problem, one can assume that all elements on the stack belong to one large structure or array. In this case none of the elements are replaceable or reorderable. Doing this, however, will inhibit any further optimizations concerning these variables since arrays and structures are often ignored by the majority of code improving transformations.

In the case of following calling conventions, there are two requirements for guaranteeing consistency without additional information. First of all, the function must be assumed to be using its entire stack for argument space, and thus it is not able to be reorganized in any way. This is merely the same requirement as above for structures and arrays. Additionally, all argument registers and return registers must be marked as live using the meta-information RTLs in appropriate places. This will serve to inhibit many of VISTA's transformation phases from improving the code. One example of this would be the inability of *dead assignment elimination* to adequately detect dead assignments to argument or return registers.

# 3.5 Additional Translators

Development of the ASM2RTL tool suite started with the SPARC architecture, since the ISA is RISC-based and thus very orthogonal. Additionally, the SPARC port of VISTA has had the most extensive testing. The SPARC however was not chosen for this study, since we expected the largest gains to be due to undoing and re-performing *register allocation*. Preliminary tests showed that the MiBench benchmarks were just too small to create a significant amount of register pressure in the SPARC's 32 integer and 32 floating point register environment.

After completing the SPARC translator, a TMS320c54x-based translator was developed. Since its main use is as a Digital Signal Processor (DSP), the ISA is CISC-based and it has several addressing modes that make accurate decoding of instructions more difficult. Unfortunately, we found that the TMS320c54x-based port of VISTA was much less robust, so additional addressing modes were added to further facilitate the translation of assembly instructions. Even so, several instructions that the native TI compiler exploited were not able to be realized within the VISTA environment. This led to significant decreases in performance, so a more appropriate embedded architecture was chosen for this study instead.

The StrongARM fits all criteria that we needed. It is an embedded processor having only 16 integer registers and 8 floating point registers. The ISA is very orthogonal with only a small number of instructions being hard to exploit by a compiler. Additionally the StrongARM port of VISTA is very robust and thus provided an excellent framework within which the proposed de-optimization strategy could be adequately evaluated.

# CHAPTER 4

## DEVELOPMENT OF DE-OPTIMIZATIONS

This chapter describes in detail the development and implementation of two new deoptimization phases to be added to the VISTA framework. Additionally the motivation for performing each de-optimization is also discussed. These de-optimizations were selected because each produces a noticeable effect depending on the phase order in which they are performed. The first de-optimization that is described deals with *loop-invariant code motion*. Next, the de-optimization of *register allocation* and *register assignment* is covered. Finally we discuss some of the implementation issues concerning the correctness of de-optimized code.

### 4.1 Loop-Invariant Code Motion